# Memory Consistency Directed Cache Coherence Protocols for Scalable Multiprocessors

Marco Elver

Doctor of Philosophy

Institute of Computing Systems Architecture

School of Informatics

University of Edinburgh

2016

#### **Abstract**

The memory consistency model, which formally specifies the behavior of the memory system, is used by programmers to reason about parallel programs. From a hardware design perspective, weaker consistency models permit various optimizations in a multiprocessor system: this thesis focuses on designing and optimizing the cache coherence protocol for a given target memory consistency model.

Traditional directory coherence protocols are designed to be compatible with the strictest memory consistency model, sequential consistency (SC). When they are used for chip multiprocessors (CMPs) that provide more relaxed memory consistency models, such protocols turn out to be unnecessarily strict. Usually, this comes at the cost of scalability, in terms of per-core storage due to sharer tracking, which poses a problem with increasing number of cores in today's CMPs, most of which no longer are sequentially consistent. The recent convergence towards programming language based relaxed memory consistency models has sparked renewed interest in lazy cache coherence protocols. These protocols exploit synchronization information by enforcing coherence only at synchronization boundaries via self-invalidation. As a result, such protocols do not require sharer tracking which benefits scalability. On the downside, such protocols are only readily applicable to a restricted set of consistency models, such as Release Consistency (RC), which expose synchronization information explicitly. In particular, existing architectures with stricter consistency models (such as x86) cannot readily make use of lazy coherence protocols without either: adapting the protocol to satisfy the stricter consistency model; or changing the architecture's consistency model to (a variant of) RC, typically at the expense of backward compatibility. The first part of this thesis explores both these options, with a focus on a practical approach satisfying backward compatibility.

Because of the wide adoption of Total Store Order (TSO) and its variants in x86 and SPARC processors, and existing parallel programs written for these architectures, we first propose TSO-CC, a lazy cache coherence protocol for the TSO memory consistency model. TSO-CC does not track sharers and instead relies on self-invalidation and detection of potential acquires (in the absence of explicit synchronization) using per cache line timestamps to efficiently and lazily satisfy the TSO memory consistency model. Our results show that TSO-CC achieves, on average, performance comparable to a MESI directory protocol, while TSO-CC's storage overhead per cache line scales logarithmically with increasing core count.

Next, we propose an approach for the x86-64 architecture, which is a compromise between retaining the original consistency model and using a more storage efficient lazy coherence protocol. First, we propose a mechanism to convey synchronization information via a simple ISA extension, while retaining backward compatibility with legacy codes and older microarchitectures. Second, we propose RC3 (based on TSO-CC), a scalable cache coherence protocol for RCtso, the resulting memory consistency model. RC3 does not track sharers and relies on self-invalidation on acquires. To satisfy RCtso efficiently, the protocol reduces self-invalidations transitively using per-L1 timestamps only. RC3 outperforms a conventional lazy RC protocol by 12%, achieving performance comparable to a MESI directory protocol for RC optimized programs. RC3's storage overhead per cache line scales logarithmically with increasing core count and reduces on-chip coherence storage overheads by 45% compared to TSO-CC.

Finally, it is imperative that hardware adheres to the promised memory consistency model. Indeed, consistency directed coherence protocols cannot use conventional coherence definitions (e.g. SWMR) to be verified against, and few existing verification methodologies apply. Furthermore, as the full consistency model is used as a specification, their interaction with other components (e.g. pipeline) of a system must not be neglected in the verification process. Therefore, verifying a system with such protocols in the context of interacting components is even more important than before. One common way to do this is via executing tests, where specific threads of instruction sequences are generated and their executions are checked for adherence to the consistency model. It would be extremely beneficial to execute such tests under simulation, i.e. when the functional design implementation of the hardware is being prototyped. Most prior verification methodologies, however, target post-silicon environments, which when used for simulation-based memory consistency verification would be too slow.

We propose McVerSi, a test generation framework for fast memory consistency verification of a full-system design implementation under simulation. Our primary contribution is a Genetic Programming (GP) based approach to memory consistency test generation, which relies on a novel crossover function that prioritizes memory operations contributing to non-determinism, thereby increasing the probability of uncovering memory consistency bugs. To guide tests towards exercising as much logic as possible, the simulator's reported coverage is used as the fitness function. Furthermore, we increase test throughput by making the test workload simulation-aware. We evaluate our proposed framework using the Gem5 cycle accurate simulator in full-system mode with Ruby (with configurations that use Gem5's MESI protocol, and our proposed

TSO-CC together with an out-of-order pipeline). We discover 2 new bugs in the MESI protocol due to the faulty interaction of the pipeline and the cache coherence protocol, highlighting that even conventional protocols should be verified rigorously in the context of a full-system. Crucially, these bugs would not have been discovered through individual verification of the pipeline or the coherence protocol. We study 11 bugs in total. Our GP-based test generation approach finds all bugs consistently, therefore providing much higher guarantees compared to alternative approaches (pseudo-random test generation and litmus tests).

#### **Lay Summary**

At the beginning of the 21st century, designers of high-performance processors found that increasing performance by increasing clock frequencies become infeasible. Further increasing clock frequencies come with unmanageable energy budgets as well as complexities in the way instructions would be processed. Yet, Moore's law is indeed still going strong, and we are seeing more and more transistors on a single chip. Consequently, this potential should not be ignored, and designers turned towards replicating the processing "cores" responsible for a single "thread" of instructions on a single chip: the result is the "multicore" chip, which can process many more threads at the same time, therefore improving overall performance.

Unfortunately, with the current designs, problems arise when attempting to scale to an order of magnitude more cores than we have today. Current state-of-the-art approaches for specific components used on a chip are simply not scalable in terms of the number of cores. One such component is the "cache coherence protocol." These days, every processing core has attached to it a small private cache to speed up memory accesses. These caches replicate data that is found in main memory. However, if two cores access the same data, then this data would be replicated in these two private caches. Now, what happens if one of these cores modifies this data and the other tries to read it? It is the coherence protocol's job to ensure there are no inconsistencies in the caches by performing various operations (sending invalidations, updates, new data, etc.).

From the programmer's point of view, caches should be transparent. The programmer, however, sticks to certain rules which specify what happens when multiple threads read and write the same data: these rules are called the "memory consistency model." The memory consistency model simply says in what order operations must become visible relative to each other. The processor must then ensure that these rules are not broken to guarantee consistency. In the mentioned case where the cores each have private caches, and the same data is replicated across them, it may suddenly be possible to violate these rules if the cache coherence protocol did not exist.

Traditional cache coherence protocols, however, do not scale well to many more cores. The reason for this is that they require maintaining metadata, which will take up too much space on a chip if more cores are added. To solve this problem, there have been several recent works which propose new cache coherence protocols which do not have this problem by eliminating the expensive metadata. The commonality among

them is, that they rely on relaxed memory consistency models (those that enforce very little ordering among instructions). Unfortunately, these proposals rely on consistency models which either are not widely used or not used at all in real processors. This limits their applicability to modern architectures used in today's and future devices, as too much existing software is too important and cannot simply stop working.

In this thesis, this new class of coherence protocol is explored in the context of real architectures, in particular, the common x86 and SPARC architectures. The consistency model found these systems is called Total Store Order (TSO). The first contribution of this thesis is called TSO-CC, a coherence protocol for TSO, which does not require the use of expensive metadata and achieves performance comparable to a traditional coherence protocol. TSO-CC achieves this via a novel technique using timestamps to limit the times when the protocol needs to perform costly maintenance on private caches.

The second contribution is RC3, a coherence protocol optimized for a more relaxed consistency model than TSO, as these types of consistency models are found in modern programming languages—ideally, the consistency models of multicores and programming languages should be aligned for optimal performance. Unlike previous approaches, the presented approach is still compatible with the x86 architecture and achieves good performance by reusing the timestamp technique—but in a limited form—from TSO-CC. Consequently, the RC3 protocol is even more efficient than TSO-CC.

Many of these techniques are usually prototyped as part of a processor simulator. In particular, the simulation of an entire computer is called a "full-system simulation." Here, the coherence protocol is only a small component of the larger system but interacts with many other components. These other components may also have an effect on the enforcement of the promised memory consistency model. In particular, some interactions between coherence protocol and processing pipeline are crucial. For the "consistency directed coherence protocols" this thesis proposes, these interactions should not be neglected; however, we found even traditional protocols are not checked sufficiently for the interaction with other components. To ensure the processor does not violate the consistency model's rules, the third and final contribution, called McVerSi, is an approach for fast verification of a full-system implemented in a processor simulator. Indeed, there is a gap in existing approaches, as they do not optimize (they are too slow) for memory consistency verification in a full-system simulation. McVerSi is filling this gap.

#### **Acknowledgements**

First and foremost, I wish to thank my advisor, Dr. Vijayanand Nagarajan, for his guidance, support and patience throughout. His advice was invaluable in helping me understanding the topics at hand and the process of research itself. Furthermore, I am extremely thankful for Vijay continually encouraging me to aim higher, as well as giving me the space to explore.

Second, I would like to thank my second supervisor, Christian Fensch. I am very thankful for his honest and critical advice, which helped me see things from different perspectives. I would also like to thank Björn Franke and Susmit Sarkar for being part of the annual review committee and their helpful suggestions. Many thanks to Babak Falsafi and Boris Grot for being on my viva panel.

On this journey, many people have supported, given advice, inspired my curiosity and/or helped in various ways—thank you! Special mention goes to: Andrew McPherson, Andrew Sogokon, Arpit Joshi, Bharghava Rajaram, Cheng-Chieh Huang, Chris Banks, Chris Margiolas, Christian Buck, Christopher Thompson, Erik Tomusk, Gabriele Farina, Harry Wagstaff, Jade Alglave, Jean-Luc Stevens, Ohad Kammar, Paul Jackson, Peter Sewell, Philipp Rüdiger, Saumay Dublish, Stephan Diestelhorst, Thibaut Lutz, Vasileios Porpodas, and everybody at ICSA.

Last, but not least, my sincere thanks to my parents for their continued support and encouragement.

#### **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified. Some of the material used in this thesis has been published in the following papers:

Marco Elver and Vijay Nagarajan, "TSO-CC: Consistency directed cache coherence for TSO", in 20th IEEE International Symposium on High Performance Computer Architecture (HPCA-20), Orlando, FL, USA, February 15-19, 2014. DOI: 10.1109/HPCA.2014.6835927

Marco Elver and Vijay Nagarajan, "RC3: Consistency directed cache coherence for x86-64 with RC extensions", in *International Conference on Parallel Architectures and Compilation Techniques (PACT '15)*, San Francisco, CA, USA, October 18-21, 2015. DOI: 10.1109/PACT.2015.37

Marco Elver and Vijay Nagarajan, "McVerSi: A Test Generation Framework for Fast Memory Consistency Verification in Simulation", in 22nd IEEE International Symposium on High Performance Computer Architecture (HPCA-22), Barcelona, Spain, March 12-16, 2016. DOI: 10.1109/HPCA.2016.7446099

(Marco Elver)

To my parents.

# **Table of Contents**

| I  | Pre  | eamble  | e                                   | 1  |

|----|------|---------|-------------------------------------|----|

| 1  | Intr | oductio | on .                                | 3  |

|    | 1.1  | Cache   | Coherence Protocol Scaling          | 3  |

|    | 1.2  | Memo    | ory Consistency and Cache Coherence | 6  |

|    | 1.3  | Contri  | ibutions                            | 7  |

|    | 1.4  | Thesis  | s Structure                         | 9  |

| II | Ba   | ackgro  | ound                                | 11 |

| 2  | Mer  | nory Co | onsistency Models                   | 13 |

|    | 2.1  | Overv   | iew                                 | 13 |

|    | 2.2  | Axion   | natic Framework                     | 14 |

|    |      | 2.2.1   | Instruction Semantics               | 14 |

|    |      | 2.2.2   | Candidate Executions                | 15 |

|    |      | 2.2.3   | Architecture Definitions            | 17 |

|    |      | 2.2.4   | Constraint Specifications           | 17 |

|    | 2.3  | Assun   | nptions on Progress Guarantees      | 18 |

|    | 2.4  | System  | m-Centric Models                    | 19 |

|    |      | 2.4.1   | Sequential Consistency              | 19 |

|    |      | 2.4.2   | Total Store Order                   | 19 |

|    |      | 2.4.3   | Release Consistency                 | 21 |

|    | 2.5  | Progra  | ammer-Centric Models                | 21 |

| 3  | Cac  | he Coh  | erence Protocols                    | 25 |

|    | 3.1  | Overv   | riew                                | 25 |

|    | 3.2  | Defini  | tion of Coherence                   | 25 |

|    | 3.3  | Baseli  | ne and Assumptions                  | 28 |

|    |     | 3.3.1   | Adding the Exclusive State                    | 31 |

|----|-----|---------|-----------------------------------------------|----|

|    | 3.4 | Eager   | versus Lazy Coherence                         | 31 |

| II | I C | Consist | ency Directed Cache Coherence Protocols       | 35 |

| 4  | TSC | -CC: C  | Consistency Directed Cache Coherence for TSO  | 37 |

|    | 4.1 | Introdu | uction                                        | 37 |

|    |     | 4.1.1   | Motivation                                    | 38 |

|    |     | 4.1.2   | Requirements                                  | 38 |

|    |     | 4.1.3   | Approach                                      | 39 |

|    | 4.2 | TSO-C   | CC: Protocol Design                           | 40 |

|    |     | 4.2.1   | Overview                                      | 40 |

|    |     | 4.2.2   | Basic Protocol                                | 42 |

|    |     | 4.2.3   | Opt. 1: Reducing Self-Invalidations           | 43 |

|    |     | 4.2.4   | Opt. 2: Shared Read-Only Data                 | 44 |

|    |     | 4.2.5   | Timestamp Resets                              | 46 |

|    |     | 4.2.6   | Atomic Accesses and Fences                    | 47 |

|    |     | 4.2.7   | Speculative Execution                         | 47 |

|    |     | 4.2.8   | Storage Requirements and Organization         | 48 |

|    | 4.3 | Proof   | of Correctness                                | 50 |

|    |     | 4.3.1   | Abstract TSO Load-Buffering Machine           | 51 |

|    |     | 4.3.2   | Sketch for Unoptimized Protocol               | 55 |

|    | 4.4 | Evalua  | ation Methodology                             | 57 |

|    |     | 4.4.1   | Simulation Environment                        | 57 |

|    |     | 4.4.2   | Workloads                                     | 57 |

|    |     | 4.4.3   | Protocol Configurations and Storage Overheads | 58 |

|    |     | 4.4.4   | Verification                                  | 61 |

|    | 4.5 | Experi  | imental Results                               | 62 |

|    |     | 4.5.1   | Discussion                                    | 67 |

|    | 4.6 | Relate  | d Work                                        | 68 |

|    |     | 4.6.1   | Coherence for Sequential Consistency          | 68 |

|    |     | 4.6.2   | Coherence for Relaxed Consistency Models      | 69 |

|    |     | 4.6.3   | Distributed Shared Memory (DSM)               | 70 |

|    | 17  | Conclu  | ucion                                         | 70 |

| 5 | RC3        | 3: Cons       | sistency Directed Cache Coherence for x86-64 with RC Exter  | n-       |

|---|------------|---------------|-------------------------------------------------------------|----------|

|   | sion       | s             |                                                             | 73       |

|   | 5.1        | Introd        | uction                                                      | 73       |

|   |            | 5.1.1         | Motivation                                                  | 74       |

|   |            | 5.1.2         | Approach                                                    | 74       |

|   | 5.2        | Limita        | ations of TSO-CC                                            | 75       |

|   | 5.3        | x86-R         | Ctso: Release Consistency for x86-64                        | 77       |

|   |            | 5.3.1         | ISA Extension Details                                       | 78       |

|   | 5.4        | RC3:          | Protocol Design                                             | 79       |

|   |            | 5.4.1         | Overview                                                    | 79       |

|   |            | 5.4.2         | Basic Protocol                                              | 80       |

|   |            | 5.4.3         | Opt. 1: Reducing Self-Invalidations of Redundant Acquires . | 82       |

|   |            | 5.4.4         | Timestamp Resets                                            | 84       |

|   |            | 5.4.5         | Opt. 2: Shared Read-Only with Epoch Based Decay             | 85       |

|   |            | 5.4.6         | Atomic Instructions and Fences                              | 86       |

|   |            | 5.4.7         | Speculative Execution                                       | 86       |

|   |            | 5.4.8         | Storage Requirements and Organization                       | 86       |

|   | 5.5        | Evalua        | ation Methodology                                           | 88       |

|   |            | 5.5.1         | Simulation Environment                                      | 88       |

|   |            | 5.5.2         | Workloads                                                   | 89       |

|   |            | 5.5.3         | Protocol Configurations and Storage Overheads               | 90       |

|   | 5.6        | Experi        | imental Results                                             | 91       |

|   | 5.7        | Relate        | ed Work                                                     | 96       |

|   |            | 5.7.1         | Language to Hardware Level Consistency                      | 96       |

|   |            | 5.7.2         | Consistency Directed Coherence                              | 97       |

|   |            | 5.7.3         | Data Structures in Eager Protocols                          | 97       |

|   | 5.8        | Concl         | usion                                                       | 98       |

| I | 7 <b>N</b> | <b>T</b> emor | ry Consistency Verification                                 | 101      |

| 1 | 14         | 1011101       | y consistency vermention                                    | 101      |

| 6 | McV        | VerSi: A      | A Test Generation Framework for Fast Memory Consistence     | <b>y</b> |

|   | Veri       |               | n in Simulation                                             | 103      |

|   | 6.1        | Introd        | uction                                                      | 103      |

|   |            | 6.1.1         | Approach                                                    | 104      |

|   | 6.2        | Evolut        | tionary Algorithms                                          | 106      |

|              | 6.3 | Test G   | eneration                                   | 106 |

|--------------|-----|----------|---------------------------------------------|-----|

|              |     | 6.3.1    | Overview                                    | 107 |

|              |     | 6.3.2    | Coverage and Fitness                        | 109 |

|              |     | 6.3.3    | Test Representation, Crossover and Mutation | 110 |

|              | 6.4 | Accele   | rating Test Execution & Checking            | 114 |

|              |     | 6.4.1    | Checker                                     | 114 |

|              |     | 6.4.2    | Complexity Implications                     | 116 |

|              | 6.5 | Evalua   | tion Methodology                            | 117 |

|              |     | 6.5.1    | Simulation Environment                      | 117 |

|              |     | 6.5.2    | Test Generation & Checking                  | 118 |

|              |     | 6.5.3    | Selected Bugs                               | 121 |

|              | 6.6 | Experi   | mental Results                              | 123 |

|              |     | 6.6.1    | Bug Coverage                                | 123 |

|              |     | 6.6.2    | Structural Coverage                         | 126 |

|              | 6.7 | Related  | d Work                                      | 127 |

|              |     | 6.7.1    | Formal Verification                         | 127 |

|              |     | 6.7.2    | Memory System Verification                  | 128 |

|              |     | 6.7.3    | Full-System Verification                    | 128 |

|              |     | 6.7.4    | Hardware Support for MCM Verification       | 129 |

|              | 6.8 | Conclu   | ısion                                       | 129 |

| $\mathbf{V}$ | Co  | nclusi   | ons                                         | 131 |

| •            | Cu  | iiciusi  | Olis                                        | 131 |

| 7            | Con | clusions | s and Future Directions                     | 133 |

|              | 7.1 | Openir   | ng Pandora's Box                            | 133 |

|              | 7.2 | Critica  | l Analysis                                  | 135 |

|              |     | 7.2.1    | Cache and Directory Organization            | 135 |

|              |     | 7.2.2    | Conversion to RCtso                         | 135 |

|              |     | 7.2.3    | Transparency of Genetic Programming         | 136 |

|              | 7.3 | Future   | Directions                                  | 136 |

|              |     | 7.3.1    | Microarchitectural Gaps and Power Modelling | 136 |

|              |     | 7.3.2    | Better Formal Verification                  | 136 |

| VI | [ <b>A</b> | ppend   | lix                              | 139   |

|----|------------|---------|----------------------------------|-------|

| A  | Deta       | iled Pr | otocol Specification for TSO-CC  | 141   |

|    | A.1        | Assum   | nptions and Definitions          | 141   |

|    | A.2        | Protoc  | ol State Transition Tables       | 141   |

|    |            | A.2.1   | Private Cache Controller         | 142   |

|    |            | A.2.2   | Directory Controller             | 142   |

|    | A.3        | Additio | onal Rules and Optimizations     | 145   |

|    |            | A.3.1   | Cache Inclusivity and Evictions  | 145   |

|    |            | A.3.2   | Timestamp Table Size Relaxations | 145   |

|    |            | A.3.3   | Effect of L1 Timestamp update    | 145   |

|    |            | A.3.4   | Effect of L2 Timestamp update    | 146   |

|    |            | A.3.5   | TimestampReset Races             | . 147 |

# **List of Tables**

| 2.1 | Definition of relations used to specify memory consistency models in |     |

|-----|----------------------------------------------------------------------|-----|

|     | the framework of [AMT14]                                             | 16  |

| 4.1 | TSO-CC specific storage requirements                                 | 49  |

| 4.2 | System parameters for TSO-CC evaluation                              | 58  |

| 4.3 | Benchmarks and their input parameters for TSO-CC evaluation          | 59  |

| 5.1 | RCtso ordering requirements                                          | 78  |

| 5.2 | RC3 specific storage requirements                                    | 87  |

| 5.3 | System parameters for RC3 evaluation                                 | 88  |

| 5.4 | Benchmarks and their input parameters for RC3 evaluation             | 89  |

| 5.5 | RC3 storage scaling                                                  | 91  |

| 6.1 | McVerSi Guest-Host interface                                         | 115 |

| 6.2 | System parameters for McVerSi evaluation                             | 118 |

| 6.3 | McVerSi test generation parameters                                   | 119 |

| 6.4 | McVerSi bug coverage                                                 | 125 |

| 6.5 | McVerSi bugs found up to 10 days                                     | 126 |

| 6.6 | McVerSi maximum total transition coverage                            | 126 |

| A.1 | TSO-CC private (L1) cache controller transition table                | 143 |

| A.2 | Directory (L2) controller transition table                           | 144 |

# **List of Figures**

| 1.1  | Baseline architecture block diagram                                   | 4  |

|------|-----------------------------------------------------------------------|----|

| 2.1  | Overview of specification and verification of multi-threaded programs |    |

|      | using axiomatic memory consistency models                             | 15 |

| 2.2  | Store buffering pattern showing forbidden executions                  | 19 |

| 2.3  | Simple mutual exclusion algorithm for SC                              | 20 |

| 2.4  | Message passing pattern showing forbidden executions                  | 20 |

| 2.5  | Relative optimization potential of various memory consistency models  | 23 |

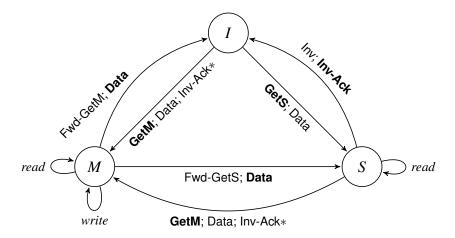

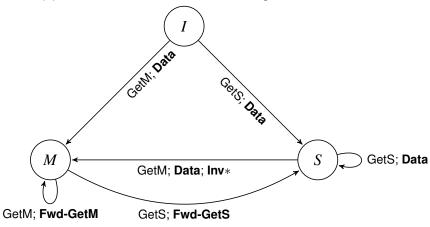

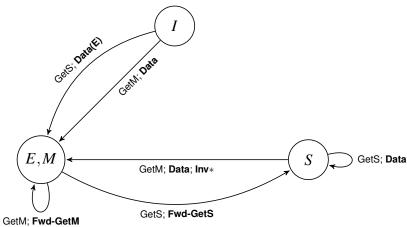

| 3.1  | Directory based MSI protocol transition diagram of stable states      | 29 |

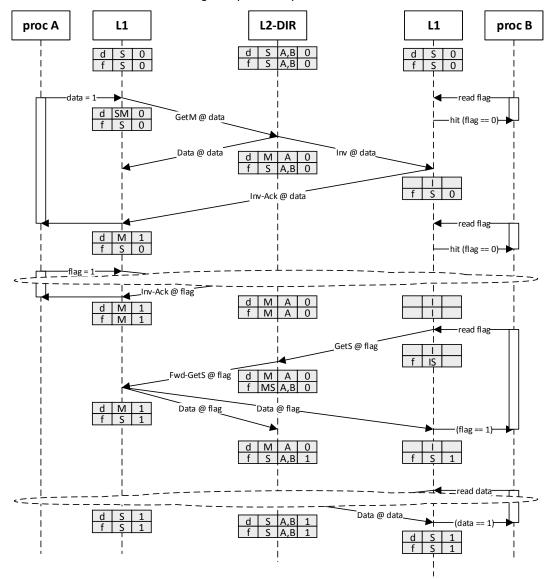

| 3.2  | An example demonstrating the MSI protocol                             | 30 |

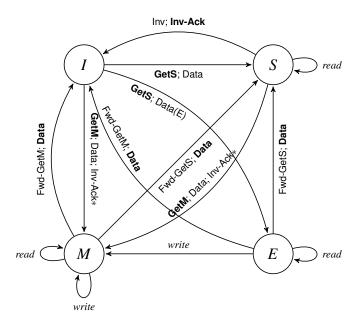

| 3.3  | Directory based MESI protocol transition diagram of stable states     | 32 |

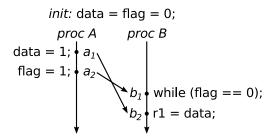

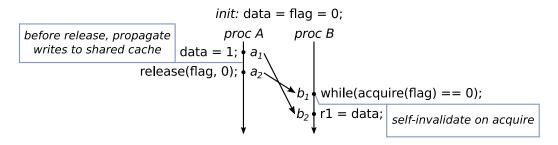

| 3.4  | Producer-consumer example with lazy RC                                | 33 |

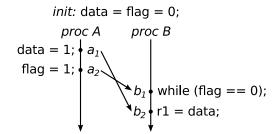

| 4.1  | Producer-consumer and TSO ordering example                            | 38 |

| 4.2  | Message passing pattern                                               | 48 |

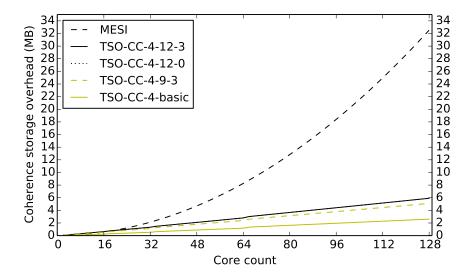

| 4.3  | TSO-CC storage scaling                                                | 60 |

| 4.4  | TSO-CC execution times                                                | 63 |

| 4.5  | TSO-CC network traffic                                                | 63 |

| 4.6  | TSO-CC L1 cache misses                                                | 64 |

| 4.7  | TSO-CC L1 cache hits and misses                                       | 64 |

| 4.8  | TSO-CC self-invalidations upon data response                          | 65 |

| 4.9  | TSO-CC RMW latencies                                                  | 66 |

| 4.10 | TSO-CC breakdown of L1 self-invalidation cause                        | 66 |

| 5.1  | Extended producer-consumer example                                    | 76 |

| 5.2  | RC3 execution times                                                   | 92 |

| 5.3  | RC3 network traffic                                                   | 92 |

| 5.4  | RC3 L1 cache misses                                                   | 93 |

| 5.5 | RC3 L1 cache hits and misses           |

|-----|----------------------------------------|

| 5.6 | RC3 normalized self-invalidations      |

| 6.1 | Message passing pattern                |

| 6.2 | McVerSi crossover and mutation example |

# Part I

# **Preamble**

### Chapter 1

#### Introduction

#### 1.1 Cache Coherence Protocol Scaling

With the breakdown of Dennard scaling [Den+74]—the end of supply voltage scaling—architects have been looking for alternatives to take advantage of the continued increase in available transistor counts as per Moore's Law [Moo65]. At the beginning of the 21st century, the trend of the industry shifted towards using multiple cores on a single chip—"multicores" or chip multiprocessors (CMPs)—to improve performance for parallel workloads. Unfortunately, scaling CMPs to ever increasing core counts also faces several challenges [Esm+11]. A major challenge is the cache coherence protocol, as conventional approaches quickly outgrow the permitted cost to achieve ever increasing core counts [Cho+11; MHS12; KK10; Kel+10; RK12].

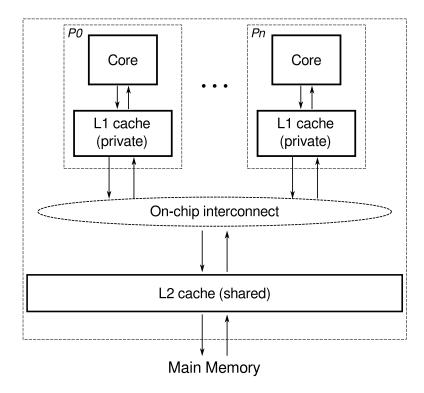

In shared memory multiprocessors, each processor typically accesses a local cache to reduce memory latency and bandwidth—Figure 1.1 illustrates a simple CMP baseline architecture. Data cached in local caches, however, can become out-of-date when they are modified by other processors. *Cache coherence* helps ensure shared memory correctness by making caches transparent to programmers, giving the illusion of a single shared address space. Shared-memory correctness is defined by the *memory consistency model* (MCM), which formally specifies in what order memory operations (reads and writes) must appear to the programmer [AG96; SHW11]: stricter models restrict reordering, whereas weaker models permit larger amounts of instruction reordering.

The relation between the processor's memory consistency model and the coherence protocol has traditionally been abstracted to the point where each subsystem considers the other as a black box [SHW11]. Generally, this is beneficial, as it reduces overall complexity; however, as a result, coherence protocols are designed to be compatible with

4. Introduction

Figure 1.1: Block diagram of baseline architecture of chip multiprocessor (CMP) system assumed.

the strictest consistency model, sequential consistency (SC). SC mandates that writes are made globally visible before a subsequent memory operation. The coherence protocol plays a crucial role in the implementation: before writing to a cache line, conventional coherence protocols propagate writes *eagerly* by invalidating shared copies in other processors.

Providing eager coherence, however, comes at a cost. A simple approach is to use snooping-based protocols, where writes to non-exclusive cache lines are effectively broadcast. Unfortunately, in snooping-based systems, the interconnect quickly becomes a bottleneck with increasing number of processors [Aga+88]. A more scalable approach is to use directory-based protocols [CF78] in which the directory maintains, for each cache line, the list of processors caching that line, in the *sharing vector*. Upon a write to a non-exclusive cache line, invalidation requests are sent to only those processors caching that line.

While avoiding the potentially costly broadcasts, the additional invalidation and acknowledgement messages nevertheless represent overhead. More importantly, the bookkeeping to maintain the list of sharers becomes prohibitively expensive with increasing number of cores (in terms of area and power). Coherence protocols need to

overcome inherent scalability issues if we wish to continue the trend of ever increasing cores. More specifically, the size of the sharing vector increases linearly with the number of processors. With an increasing number of processors, it becomes prohibitively expensive to support a sharing vector for large-scale CMPs [Cho+11; MHS12; KK10; Kel+10; RK12].

In the foreseeable future, on-chip cache coherence will continue to play an important role in continuing to provide programmers an intuitive view of shared memory, but several *scaling challenges* need to be overcome [MHS12]:

- on-chip storage requirements;

- on-chip network traffic;

- inefficiencies caused by maintaining cache inclusion (e.g. false sharing);

- latency of cache misses;

- energy overheads.

Over the years, many approaches have addressed some of these challenges, especially by optimizing the data structures and cache organization [Cue+11; Fer+11; GWM90; MHS12; Pug+10; SK12; Wal92; ZSD10]. But the alternative, of optimizing the protocol itself, in particular for a particular memory consistency model, has not been explored sufficiently for modern systems. Recent years have seen renewed interest in this approach via *lazy* cache coherence protocols [ADC11; Cho+11; FC08; KK10; RK12; SKA13; SA15], highlighting its potential—however, these approaches target relaxed consistency models with explicitly exposed synchronization, e.g. Release Consistency (RC) [Gha95]. Lazy coherence protocols shift the task of invalidation from the writer to the reader via *self-invalidation* at synchronization boundaries [LW95].

This thesis focuses on the design of memory consistency directed cache coherence protocols, in particular for consistency models and architectures which *do not explicitly expose synchronization* to overcome some of the above challenges. This approach, however, makes it less straightforward to reason in terms of established properties of coherence (e.g. Single-Writer–Multiple-Reader [SHW11]): in the approach taken in this thesis, the property to be satisfied *is* the consistency model of the *full* system. In the final part of this thesis, a framework for fast simulation-based memory consistency verification is proposed to help designers verify *full-system* implementations of a design.

6 1. Introduction

#### 1.2 Memory Consistency and Cache Coherence

The memory consistency model specifies the permitted reordering of memory operations, with which the programmer can then reason about parallel program correctness [AG96; SHW11]. Although more relaxed memory consistency models are less intuitive from a programmer perspective, they can be motivated by performance optimizations in the implementation of a shared memory multiprocessor system. For example, write-buffers, in the absence of any other visible optimizations, give rise to Total Store Order (TSO), as in e.g. x86 [OSS09], where writes may appear to be reordered after following reads.

Broadly, the relationship between memory consistency model to cache coherence protocol is a specification to a part of its implementation; indeed, there are many other components in a system, e.g. core pipeline, and the combination of all components gives rise to the final consistency model. Here, the coherence protocol is responsible for the propagation of data in the memory hierarchy, in particular, between caches to make replicated data in independent caches appear as part of a single shared memory.

Yet, the classical definition of cache coherence is not tied too closely to the memory consistency model, but rather has various other definitions. One common definition is, that coherence must enforce the following invariant: per memory location, there must only be either a single writer (and no readers) or there may be several readers (but no writers)—also referred to as the Single-Writer–Multiple-Reader (SWMR) invariant [SHW11]. Indeed, this definition is sufficient for most traditional coherence protocols, as well as strict enough to guarantee compatibility with SC (in the presence of an in-order pipeline) [MS09].

As a result, conventional coherence protocols propagate writes *eagerly* by invalidating shared copies of data in other processors (before the write). To achieve this, protocols can either be snooping (interconnect bottleneck [Aga+88]) or use a directory tracking sharers (storage bottleneck [Cho+11; MHS12; KK10; Kel+10; RK12]). However, *modern CMPs no longer guarantee SC* (see ARM [AMT14; Flu+16], POWER [Sar+11], SPARC [SPA92], x86 [OSS09])—the main contributing factor being core pipeline optimizations, but not the coherence protocol.

**Hypothesis:** If modern CMPs no longer guarantee SC, is using coherence protocols designed to satisfy a model as strict as SC still required? And in relaxing this requirement, can more scalable protocols be designed? The main hypothesis of this thesis is, that cache coherence protocols can be optimized for a target consistency model (weaker than SC), and in doing so address several of the scaling challenges—the main focus of this

1.3. Contributions 7

thesis being storage overheads while retaining baseline performance characteristics.

Finally, *verification* of cache coherence is an important aspect of design [ASL03]. Designing coherence protocols satisfying invariants such as SWMR (and thus be compatible with SC), is also beneficial for verification: indeed, using SWMR as a key invariant is straightforward to use in formal methods approaches such as model checking [PD97]. One direction is to design protocols with verifiability (using existing verification methodologies) in mind [Zha+14]. The other direction is to explore alternative verification methodologies to suit coherence protocols that may no longer satisfy SWMR. In particular, using the final system memory consistency model to be verified against, instead of indirect invariants. Furthermore, while verifying individual components like the coherence protocol is essential, the interaction between components (pipeline, coherence protocol, etc.) in a *full-system* should not be neglected. Currently, there is a lack of methodologies for memory consistency verification of a full-system in a pre-silicon environment (e.g. simulation): can we design a methodology that decreases the time to find as many bugs as possible pre-silicon (compared to alternatives)?

#### 1.3 Contributions

Consistency Directed Cache Coherence Protocols: Existing lazy coherence cache coherence protocols [ADC11; Cho+11; FC08; KK10; RK12; SKA13; SA15] have limitations regarding portability. As they target relaxed consistency models explicitly exposing synchronization to the hardware, e.g. Release Consistency (RC) [Gha95], existing architectures with stricter models cannot benefit from them, as *legacy codes must continue to work*. Here, we consider the x86 and SPARC architectures which support variants of Total Store Order (TSO) [OSS09; SPA92]. The key challenge in designing a lazy coherence protocol for TSO is the absence of explicit *release* or *acquire* instructions; regular loads and stores have acquire and release semantics respectively.

The first contribution is **TSO-CC**, a coherence protocol that enforces TSO lazily without a full sharing vector. Without tracking sharers, the protocol must self-invalidate potentially stale cache lines upon potential acquires. In the most basic version of the protocol, every cache miss is assumed to be a potential acquire; in the *optimized* version of the protocol, we use *transitive reduction* to limit potential acquires, and therefore reduce costly self-invalidations. The use of a full sharing vector is an important factor that could limit scalability, which we overcome in our proposed protocol while *maintaining good overall performance in terms of execution times and on-chip network-traffic*.

8 1. Introduction

TSO-CC's storage overhead per cache line scales logarithmically with increasing core count. More specifically, for 32 (128) cores, our best performing configuration reduces the storage overhead over a MESI baseline protocol by 38% (82%). Our experiments with programs from SPLASH-2, PARSEC and STAMP benchmarks show an average reduction in execution time of 3% over the baseline, with the best case outperforming the baseline by 19%.

Next, we explore a method to distinguish synchronization and data operations in the x86-64 architecture to exploit the explicit synchronization information that is already present in many recent language level memory consistency models (e.g. C11 [ISO11a], C++11 [ISO11b; BA08] and Java [MPA05]). The key contribution is RC3, a lazy cache coherence protocol for RCtso, and a seamless approach to adopt the protocol in the x86-64 architecture—thereby allowing the architecture to exploit the explicit synchronization information present in many recent language level memory consistency models. We achieve this by showing how to convey explicit ordinary and synchronization information to the hardware via a backward and forward compatible<sup>1</sup> ISA extension, and in doing so propose to change the consistency model from x86-TSO to x86-RCtso. The RC3 protocol then targets the RCtso consistency model lazily, without the need for a sharing vector nor per cache line timestamps. In comparison to a conventional lazy RC coherence protocol, RC3 achieves a 12% performance improvement on average owing to transitive reduction of redundant acquires using timestamps. In comparison to TSO-CC, RC3 reduces coherence storage requirements by 45% by eliminating per cache line L1 and L2 timestamps. Furthermore, eliminating per cache line timestamps also simplifies cache accesses as timestamps do not need to be tagged.

**Full-System Memory Consistency Verification:** Simulation of a design is available much earlier in the development cycle (pre-silicon). As such it is much cheaper if as many bugs as possible are found early. Furthermore, the added observability in simulation makes debugging more straightforward. For example, the advantages of simulation for memory system verification using user-guided random tests have been described and exploited by Wood et al. [WGK90]. Unfortunately, throughput (in terms of instructions executed in wall-clock time) of an accurate simulated system is orders of magnitude lower than a real chip. The challenge is, *how do we automatically generate efficient memory consistency tests for simulation, such that the wall-clock time to explore rare corner cases and find bugs is reduced?*

<sup>&</sup>lt;sup>1</sup>Forward compatible meaning that new program codes can also still be run on old architectures.

Here, the focus lies on automated simulation-based verification of a full-system design implementation: we propose McVerSi, a test generation framework for fast, coverage directed memory consistency verification in simulation. Using a Genetic Programming (GP) [Koz92] based approach, we show how to generate tests for a full-system simulation that achieve improved test quality specifically for memory consistency verification, and also achieve greater coverage of the system (exploring rare corner cases): focusing on both these aspects leads to significantly reduced wall-clock time to find all studied bugs consistently (in comparison with alternative approaches). We evaluate McVerSi using the Gem5 [Bin+11] cycle accurate simulator in x86-64 full-system mode with Ruby (with implementations of a MESI variant and TSO-CC). Our evaluation also highlights the importance of verifying conventional protocols in the context of a full-system, as two new bugs in the MESI coherence protocol implementation of Gem5 have been found in the process.<sup>2</sup> In total, we study 11 bugs. In comparison with a pseudo-random test generator, and diy [Alg+12] generated litmus tests for TSO, our GP-based approach finds all bugs consistently within practical time bounds, thereby providing much higher bug finding guarantees.

#### 1.4 Thesis Structure

The background required is summarized in the following Part II: Chapter 2 introduces memory consistency models, and Chapter 3 defines cache coherence protocols and their role in enforcing the consistency model. Part III introduces consistency directed cache coherence protocols, the main theme of this thesis: Chapter 4 proposes TSO-CC, followed by Chapter 5 introducing RC3. Both chapters are relatively self-contained, but for a greater appreciation of RC3, it is recommended that Chapter 4 (TSO-CC) be read first. The next part is on verification, and Chapter 6 proposes the McVerSi framework. Chapter 6 is sufficiently self-contained that Part III is not a necessary dependency, but is suggested to better understand the challenges McVerSi wishes to address, as well as details of the evaluation where TSO-CC is used as a case study. Finally, Chapter 7 concludes and provides perspectives on future directions.

<sup>&</sup>lt;sup>2</sup>Fixes for the bugs have been sent to the Gem5 maintainers.

# Part II

**Background**

# **Chapter 2**

# **Memory Consistency Models**

#### 2.1 Overview

Programming shared memory multiprocessor systems correctly requires a precise definition of the *semantics* of such a system. In particular, the programmer must be aware of the memory access ordering guarantees the hardware provides. The memory consistency model (MCM) *formally specifies* the ordering guarantees with which the programmer can reason about parallel programs [AG96].

Over the years, various formalizations of MCMs have emerged. Both *axiomatic*—e.g. Sequential Consistency (SC) [Lam79], Total Store Order (TSO) [AMT14; SPA92], Release Consistency (RC) [Gha95; Gha+90], POWER [Alg+12; AMT14; Mad+12] and ARMv7 [AMT14]—as well as *operational* models—e.g. x86-TSO [OSS09], POWER [Sar+11]) and ARMv8 [Flu+16]—can be used to describe MCMs formally.

Axiomatic models present the model in terms of relations ordering operations as they may be observed, effectively forming a data-flow graph; these graphs should not be cyclic, as this would imply a contradiction and the programmer could no longer reason about their multi-threaded program. Operational models, on the other hand, are presented as abstract machines that if given a multi-threaded program, generate all allowable results. Both are important in their own right, as the former is more concise whereas the latter can give rise to more elegant proofs (e.g. Chapter 4 will introduce an operational model as a proof tool).

While there are various options for deciding upon a specific memory consistency model in a multiprocessor system, it is essential to find the right balance between programmability and performance. This section also provides an overview of the hierarchical approach to memory consistency, and how the choice of the memory consistency model impacts the implementation [Gha+90; Adv93; AH90; Gha95].

#### 2.2 Axiomatic Framework

This section summarizes the framework proposed by Alglave, Maranget, and Tautschnig [AMT14] to specify the axiomatic semantics of memory consistency models. We have chosen to use this framework, as it (1) is succinct while eliminating ambiguity (especially for the purpose of implementing decision procedures) and (2) is flexible enough to describe a variety of consistency models while relying on a library of common reusable definitions (hence a framework).

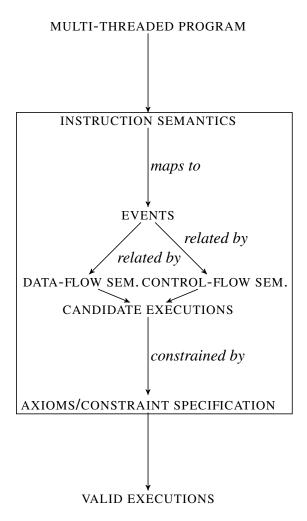

Frameworks have their disadvantages (no size fits all), but the advantages of relying on a proven framework with the ability to turn these definitions into a consistency model checker (required for Chapter 6) outweigh. Figure 2.1 illustrates the flow of how axiomatic consistency models are used in specification and verification of multi-threaded program behavior.

**Notation:** The models are described using classic set theory. As the relations capture order among events, we often use the more intuitive shorthand:  $x \stackrel{\text{rel}}{\to} y \triangleq (x,y) \in \text{rel}$ . The shorthand  $r_1; r_2$  denotes the sequential composition of two relations:  $(x,y) \in (r_1; r_2) \triangleq \exists z.(x,z) \in r_1 \land (z,y) \in r_2$ . The predicate irreflexive(r) is true iff r is irreflexive:  $\text{irreflexive}(r) \triangleq \neg(\exists x.(x,x) \in r)$ . The predicate acyclic(r) is true iff the transitive closure of r is irreflexive:  $\text{acyclic}(r) \triangleq \text{irreflexive}(r^+)$ . The reflexive-transitive closure of r is written as  $r^*$ .

#### 2.2.1 Instruction Semantics

An ISA may have a diverse set of instructions, and different instructions when executed may result in the same *effect on the memory system*. Given a multi-threaded program, and some instruction semantics, each instruction is mapped to a set of *events*. This helps to avoid redundancies and simplify the presentation of a particular memory consistency models.

**Definition 2.1** (Events). Events are unique, referred to with a lower case letter (e.g. e). An event captures the thread  $(\operatorname{proc}(e))$ , address  $(\operatorname{addr}(e))$  and action. For all events in a program, WR, WW, RR, RW are the relations capturing all write-read, write-write, read-read and read-write pairs respectively.

15

Figure 2.1: Overview of specification and verification of multi-threaded programs using axiomatic memory consistency models.

To ease the rest of the discussion, unless otherwise specified, we will assume the following generic mapping:

- Loads map to exactly one read event.

- Stores map to exactly one write event.

As much of the discussion is not specific to a particular ISA, we will refer to reads and writes rather than loads and stores where the mapping is obvious from the context. For a complete account of instruction semantics we refer to reader to [AMT14].

#### 2.2.2 Candidate Executions

A candidate execution captures one possible execution of a multi-threaded program. Depending on the control-flow and data-flow semantics, there may be a large set of

Table 2.1: Definition of relations used to specify memory consistency models in the framework of [AMT14].

| Relation | Name            | Source       | Subset of                      | Definition                                                                                                            |

|----------|-----------------|--------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| ро       | program-order   | execution    | $\mathbb{E} \times \mathbb{E}$ | instruction order lifted to events                                                                                    |

| rf       | read-from       | execution    | WR                             | links a write w to a read r taking its                                                                                |

|          |                 |              |                                | value from w                                                                                                          |

| со       | coherence       | execution    | ww                             | total order over writes to the same                                                                                   |

|          |                 |              |                                | memory location                                                                                                       |

| ppo      | preserved pro-  | architecture | ро                             | program order maintained by the ar-                                                                                   |

|          | gram order      |              |                                | chitecture                                                                                                            |

| fences   | fences          | architecture | ро                             | events ordered by fences                                                                                              |

| prop     | propagation     | architecture | ww                             | order in which writes propagate                                                                                       |

| po-loc   | program order   | derived      | ро                             | po-loc ≜                                                                                                              |

|          | subset of same  |              |                                | $\left\{ (x,y) \mid x \xrightarrow{po} y \land addr(x) = addr(y) \right\}$                                            |

|          | address events  |              |                                | ,                                                                                                                     |

| com      | communications  | derived      | $\mathbb{E} 	imes \mathbb{E}$  | $com \triangleq co \cup rf \cup fr$                                                                                   |

|          | or conflict or- |              |                                |                                                                                                                       |

|          | ders            |              |                                |                                                                                                                       |

| rfe      | read-from ex-   | derived      | rf                             | rfe ≜                                                                                                                 |

|          | ternal          |              |                                | $\left  \ \left\{ (w,r) \mid w \stackrel{rf}{\to} r \land proc(w) \neq proc(r) \right\} \ \right $                    |

| fr       | from-read       | derived      | RW                             | links reads to writes based on ob-                                                                                    |

|          |                 |              |                                | served rf and co: fr $\triangleq$ (rf <sup>-1</sup> ;co) $\triangleq$                                                 |

|          |                 |              |                                | $\left\{ (r,w) \mid \exists w'.w' \stackrel{rf}{\to} r \land w' \stackrel{co}{\to} w \right\}$                        |

| fre      | from-read ex-   | derived      | fr                             | fre ≙                                                                                                                 |

|          | ternal          |              |                                | $\left  \left. \left\{ (r,w) \mid r \stackrel{fr}{\rightarrow} w \land proc(r) \neq proc(w) \right\} \right. \right $ |

| hb       | happens before  | derived      | $\mathbb{E} \times \mathbb{E}$ | $hb \triangleq ppo \cup fences \cup rfe$                                                                              |

possible executions (but not all of which may be valid as per the constraint specification).

**Definition 2.2** (Candidate executions). A candidate execution is a tuple  $(\mathbb{E}, po, rf, co)$ , with the set of events  $\mathbb{E}$  in the program, and the relations program-order po (via control-flow semantics), reads-from rf and coherence (or write-serialization) order co (via data-flow semantics); see Table 2.1 for details.

#### 2.2.3 **Architecture Definitions**

An architecture defines the architecture specific details of a particular memory consistency model, and is used by the constraint specification to decide if a particular execution is valid or not. An architecture is defined by the tuple of relations (ppo, fences, prop), preserved program-order ppo, fences and propagation prop; see Table 2.1 for details. In the following we will provide the instantiations of Total Store Order (TSO) and Sequential Consistency (SC) as provided by [AMT14]. Both models are discussed informally in §2.4.

**Definition 2.3** (Sequential Consistency). No relaxations are permitted and all four possible instruction orderings (read-read, read-write, write-read, write-write) must be maintained.

ppo

$$\triangleq$$

po

fences  $\triangleq$   $\emptyset$

prop  $\triangleq$  ppo  $\cup$  fences  $\cup$  rf  $\cup$  fr

**Definition 2.4** (Total Store Order). Only the write to read ordering is relaxed. Reads to the same address as a preceding writes w by the same thread must observe either w or a write by another thread that happened after w in co; this, however, has no effect on the required visibility by other threads, which implies that prop only includes rfe (and not rf). The relation mfence captures write-read pairs separated by a fence instruction.

ppo

$$\triangleq$$

po \ WR

fences  $\triangleq$  mfence

prop  $\triangleq$  ppo  $\cup$  fences  $\cup$  rfe  $\cup$  fr

#### 2.2.4 **Constraint Specifications**

Given a candidate execution and an architecture specification, the constraints (or axioms) decide if the execution is valid under the complete model.

**Definition 2.5** (SC PER LOCATION). Satisfied if acyclic(po-loc∪com). SC PER LOCATION ensures that communications/conflict orders com cannot contradict program-order per memory location po-loc.<sup>1</sup>

**Definition 2.6** (NO THIN AIR). Satisfied if acyclic(hb). This constraint ensures that the happens-before order hb, which captures preserved program-order ppo, fenced

<sup>&</sup>lt;sup>1</sup>This constraint by itself is one of the definitions of coherence, as discussed in §3.2.

instructions fences, but also reads from other threads rfe is not contradictory. Effectively, this prevents reads from observing values "out of thin air", i.e. before they appear to have been written by some other thread.

**Definition 2.7** (OBSERVATION). Satisfied if irreflexive(fre; prop; hb\*). OBSER-VATION constrains the values a read may observe. Assume a write  $w_a$  to address a, a write  $w_b$  to address b, which are ordered in prop ( $w_a \stackrel{\text{prop}}{\rightarrow} w_b$ ), and a read  $r_b$  reading from  $w_b$  ( $w_b \stackrel{\text{rf}}{\rightarrow} r_b$ ), then any read  $r_a$  that happens after  $r_b$  ( $r_b \stackrel{\text{hb}}{\rightarrow} r_a$ ) cannot read from a write before  $w_a$ .

**Definition 2.8** (PROPAGATION). Satisfied if  $acyclic(co \cup prop)$ . This constraint imposes restrictions on the order in which writes are propagated to other threads, i.e. ensuring that the propagation order prop does not contradict coherence (write-serialization) order co. This constraint and depending on the prop order defines if the consistency model is *write/multi-copy atomic*, i.e. if all threads observe writes in the same order or not.

## 2.3 Assumptions on Progress Guarantees

It should be noted that most models focus on ordering constraints, however, when memory operations propagate to other threads is usually not explicit: unless specified, it is implicitly assumed that operations eventually become visible (eventual write propagation); furthermore, it is sufficient for only conflicting operations, i.e. synchronization, to eventually become visible [Gha95]. This guarantee is necessary for programs to make useful progress.

Indeed, when reasoning about a concurrent system, two types of properties should be proved: *safety* ("nothing bad will happen") and *liveness* ("something good will happen eventually") [Lam77; AS85]. In the context of multithreaded programs, the programmer asserts safety with the help of the ordering guarantees imposed by the memory consistency model, but liveness also requires guarantees on eventual write propagation.

Few consistency models place a concrete time bound or fairness restrictions on write propagation, implying that programmers must design algorithms taking this into account. A notable exception is the bounded staleness TSO model (TSO[S]) proposed by Morrison and Afek [MA14].

## 2.4 System-Centric Models

System-centric memory consistency models expose the direct interface with the hard-ware. In more relaxed consistency models, it becomes more difficult for programmers to reason about parallel programs, and as such, stricter models are preferred when programmers are expected to reason at the hardware level. This section briefly summarizes three system-centric models which will be central to later chapters.

## 2.4.1 Sequential Consistency

Sequential Consistency (SC) was first defined by Lamport [Lam79]. In SC, no relaxations are permitted and all four possible instruction orderings (read-read, read-write, write-read, write-write) must be preserved. In the words of Lamport [Lam79], a multiprocessor system can be called *sequentially consistent* if "the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program." See Definition 2.3 for the formal definition.

Consider the pattern in Figure 2.2. Here, SC forbids the case where both reads return the initial value. With a simple mutual exclusion algorithm (e.g. Dekker follows this pattern [Sco13]) as shown in Figure 2.3, this implies that the critical section cannot be entered by both threads at the same time.

| init: $x = 0, y = 0$              |          |  |

|-----------------------------------|----------|--|

| Thread 1                          | Thread 2 |  |

| x ← 1                             | y ← 1    |  |

| r1 ← y                            | r2 ← x   |  |

| SC forbids: $r1 = 0 \land r2 = 0$ |          |  |

Figure 2.2: Store buffering pattern showing forbidden executions.

#### 2.4.2 Total Store Order

Since Total Store Order (TSO) is the memory consistency model found in x86 processors, its various implementations have been analyzed in detail [OSS09]. Historically, TSO has been the result of taking writes out of the critical path and entering committed writes into a FIFO write-buffer, potentially delaying a write to cache or other parts of

| init: $x = 0$ , $y = 0$ |                    |  |

|-------------------------|--------------------|--|

| Thread 1                | Thread 2           |  |

| x ← 1                   | y ← 1              |  |

| if (y == 0) then        | if $(x == 0)$ then |  |

| critical section        | critical section   |  |

| else                    | else               |  |

Figure 2.3: Simple mutual exclusion algorithm for SC [Lam79].

| init: $x = 0, y = 0$                    |                   |  |

|-----------------------------------------|-------------------|--|

| Thread 1                                | Thread 2          |  |

| x ← 1                                   | r1 ← y            |  |

| y ← 1                                   | $r2 \leftarrow x$ |  |

| SC & TSO forbids: $r1 = 1 \land r2 = 0$ |                   |  |

Figure 2.4: Message passing pattern showing forbidden executions.

the memory hierarchy [OSS09; SC97]. Reads to the same address as prior writes by the same processor must not be affected, which mandates that reads *bypass* the write-buffer. Consequently, this relaxes the write to read ordering. See Definition 2.4 for the formal definition. As every write can potentially be a release, each write needs to *eventually* propagate to other processors, so that they are made visible to a matching acquire and forward progress is possible (see §2.3).

Figure 2.4 illustrates a common pattern where TSO (and SC) still provides intuitive semantics due to maintaining the write-write ordering. However, since write-read is now relaxed, the case forbidden under SC in Figure 2.2 is indeed valid under TSO. Consequently, this implies that the simple mutual exclusion algorithm in Figure 2.3 no longer works correctly; to make such an algorithm work again, modern architectures that provide variants of TSO, e.g. x86, need to extend TSO to provide explicit fence instructions enforcing ordering where required.

Furthermore, TSO guarantees that writes become visible to other threads at the same time—this is also referred to as *write atomicity* or *multi-copy atomicity*. This is what differentiates TSO from a related model, Processor Consistency (PC) [Gha+90], which does not mandate write/multi-copy atomicity.

#### 2.4.3 Release Consistency

A relaxed and relatively simple model which explicitly exposes synchronization operations via special instructions is Release Consistency (RC) [Gha95; Gha+90]. In RC, special *release* and *acquire* instructions are used to enforce an ordering with other memory operations in program order.

Given a write-*release*, all memory operations prior must be visible before the write; a read-*acquire* enforces preserving the program ordering of all operations after it. In addition, releases guarantee eventual propagation of synchronization data so that they become visible to corresponding acquires. The particular RC-variant imposes additional restrictions on ordering between synchronization, e.g. RCsc requires that all possible orderings between synchronization are maintained.

**Definition 2.9** (RCsc). Let AM be the relation linking all acquires a to all events e:  $MS \triangleq \{(a,e) \mid (a,e) \in \mathbb{E} \times \mathbb{E} \land \mathtt{is\_acquire}(a)\}$ . Let MS be the relation linking all events e to a write-release s:  $MS \triangleq \{(e,s) \mid (e,s) \in \mathbb{E} \times \mathbb{E} \land \mathtt{is\_release}(s)\}$ . RCsc is instantiated as follows:

ppo

$$\triangleq (po \cap AM) \cup (po \cap MS)$$

fences  $\triangleq \emptyset$

prop  $\triangleq ppo \cup fences \cup rfe \cup fr$

With RC, if the operations in the pattern of Figure 2.4 were all marked as ordinary, all executions would be valid. To only observe the same valid executions as TSO (or SC), it would be required to explicitly mark the write and read of y as release and acquire respectively.

## 2.5 Programmer-Centric Models

While many commercial multiprocessor systems adopt very relaxed memory consistency models, giving architects fewer restrictions on optimizations, this usually complicates reasoning about parallel programs at the hardware level. This problem, however, can be solved if we assume that the programmer does not need to reason about programs using the system-centric consistency models, and instead is exposed to a higher level abstraction at the programming language level [AG96].

The only requirement of the hardware level consistency model then is that any language level consistency model can be mapped to the hardware level. The formal basis

for this approach can be found in Adve et al.'s *data-race-free* [Adv93; AH90; AH93] (DRF) and Gharachorloo et al.'s *properly-labeled* [Gha95; Gha+90] (PL) models. In essence, the programmer explicitly labels synchronization and data operations correctly. In return, the system (compiler and hardware) guarantees SC—often referred to as *SC for DRF*.

Modern programming languages are converging towards clearly defined memory consistency models, and as such, the programmer only needs to reason in terms of the language level consistency model. For instance, C++11 is an adaptation of *data-race-free-0* [BA08]. However, for hardware to be able to benefit from the explicit synchronization information, the hardware's consistency model should be able to distinguish between synchronization and data operations. A straightforward implementation of *data-race-free-0* is using RC [Gha+90] (without nsync) [Adv93], where data operations are mapped to ordinary loads and stores, and synchronization operations are mapped to acquires and releases.

As a result, the hardware benefits from additional opportunity for optimization, and in particular, coherence protocol implementations can be *lazy* (§3.4). Propagation of ordinary memory operations can be delayed until an order can be re-established at synchronization boundaries [DSB86; KSB95; SD87]. This permits the protocol to remove the costly data structures to maintain a list of sharers, i.e. the sharing vector, and instead rely on self-invalidation upon synchronization boundaries as demonstrated by numerous prior works [KSB95; Cho+11; RK12; SKA13; KCZ92].

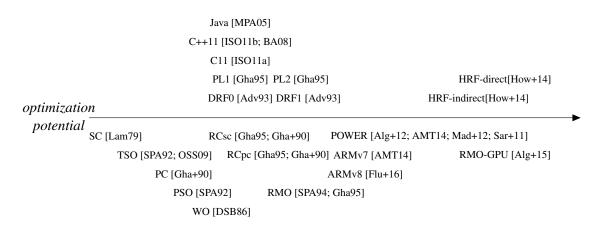

Finally, Figure 2.5 provides an overview of various memory consistency models and their relative optimization potential. Weaker consistency models generally present more opportunity for hardware optimizations. An efficient mapping from language to hardware level can be achieved, i.e. preserving as much opportunity for optimization as possible, if the system-centric model can preserve at least as much information about allowable memory operation reordering as the programmer-centric model.

#### **Programmer-centric**

#### **System-centric**

Figure 2.5: Relative optimization potential of various memory consistency models. An efficient mapping from language to hardware level can be achieved if the system-centric model can preserve at least as much information about allowable memory operation reordering as the programmer-centric model.

## **Chapter 3**

## **Cache Coherence Protocols**

#### 3.1 Overview

Since modern multiprocessors use caches to hide memory access latencies (assuming an architecture like in Figure 1.1), each core may have its own local cache (L1). With separate L1s caching the same data, modifications to this data may result in a different view of these memory locations. The role of cache coherence is then, to ensure that caches become invisible (as is the case in a uniprocessor) to the programmer. Ultimately, the programmer should only worry about the memory consistency model to write correct parallel programs as discussed in Chapter 2. As a corollary, we may argue that the cache coherence protocol is a vital component in the enforcement of the target consistency model. However, there exist several definitions of cache coherence, which we discuss in §3.2. Following that, an overview of various classes of implementations for coherence protocols are discussed (§3.4).

#### 3.2 Definition of Coherence

**Classical Definitions:** What exactly is *coherence*, and what is the relationship to the memory consistency model? A variety of (partly overlapping) definitions exist [SHW11; Gha95; HP07], on what may be called a "cache coherence protocol."

**Definition 3.1** (Coherence Invariants: SWMR and DV [SHW11]). Sorin, Hill, and Wood [SHW11] establish the following invariants to be satisfied by a coherent system.

1. Single-Writer-Multiple-Reader (SWMR) Invariant. For any memory location A, at any given (logical) time, there exists only a single core that may write to A

(and can also read it) or some number of cores that may only read A.

2. **Data-Value (DV) Invariant.** The value of the memory location at the start of an epoch is the same as the value of the memory location at the end of its last read-write epoch.

The above definition is very implementation centric, but sufficient to capture the essential properties of traditional eager coherence protocols. Sticking to this definition, however, does not make it intuitive to design lazy coherence protocols (§3.4). Indeed, some of these protocols may violate the above definition but still satisfy the below definitions and/or the target memory consistency model (as we will see later).

**Definition 3.2** (Coherence guarantees SC per memory location [SHW11]). Furthermore, Sorin, Hill, and Wood [SHW11] provides the following alternative consistency-like definition of coherence: a coherent system must appear to execute all threads' loads and stores to a single memory location in a total order that respects the program order of each thread.

This definition is arguably much more abstract than Definition 3.1, but also much broader in its scope for optimization. In fact, this definition is part of even the weakest consistency models [AMT14, §4.2 SC PER LOCATION]. For example, although SWMR is violated by the protocols in Part III, Definition 3.2 is not (as otherwise TSO would have been violated).

**Definition 3.3** (Coherence propagates and serializes per-location writes [SHW11; Gha95]). As defined by [Gha+90; Gha95] and summarized in [SHW11], coherence guarantees:

- (1) every store is eventually made visible to all cores;

- (2) writes to the same memory location are serialized (i.e., observed in the same order by all cores).

This definition again seems broader than the previous definitions. Here, the inclusion of eventual write propagation is arguably an important insight, as it is necessary to guarantee useful progress (liveness) of multithreaded programs (see §2.3). The second clause on write serialization is only a necessary condition for achieving SC per location (Definition 3.2), but not equivalent; crucially, it lacks any notion of program order.

**Definition 3.4** (Coherence preserves program order, propagates and serializes per-location writes [HP07]). Hennessy and Patterson [HP07] defines coherence as follows: *a memory system is coherent if*

- (1) a read by a processor P to a location X that follows a write by P to X, with no writes of X by another processor occurring between the write and the read by P, always returns the value written by P;

- (2) a read by a processor to location X that follows a write by another processor to X returns the written value if the read and write are sufficiently separated in time and no other writes to X occur between the two accesses;

- (3) writes to the same location are serialized; [...].

Finally, the last definition given by Hennessy and Patterson [HP07] largely overlaps with Definition 3.3. Requirement (2) of a read returning a write if they are "sufficiently separated in time" can be likened to the eventual write propagation requirement (1) of Definition 3.3. Constraint (3) of Definition 3.4 is equivalent to (2) of Definition 3.3.

Any of these definitions may be seen as the most basic *specification* of the properties that any given protocol must meet to be a correct coherence protocol implementation. In particular, as Definition 3.1 is formulated as an invariant that does not depend on the full execution history of a system, but rather in terms of access permissions or limited state, this definition seems more intuitive for a designer of a protocol. For this reason, unlike the consistency-like Definitions 3.2, 3.3 and 3.4, the use of Definition 3.1's invariants also make formal verification (e.g. model checking) of coherence protocols a more tractable problem (see §6.7).

The above definitions seem sufficient to capture the properties of *conventional hardware coherence protocols*, without having to understand the promised memory consistency model of the system in detail. And in turn, these definitions are strict enough, that meeting them provides compatibility with all common consistency models, in particular the lowest common denominator, SC. Of course, the final consistency model is subject to more than just the coherence protocol, especially the core's pipeline (e.g. write-buffers in TSO; see §2.4.2). But, with a core pipeline presenting loads and stores in program order to the memory system, and a coherence protocol satisfying the above definitions, the final consistency model provided will be SC [MS09].

**Blurring the Line:** However, certain protocols may violate some of the above invariants without violating the desired consistency model. For example, lazy coherence protocols

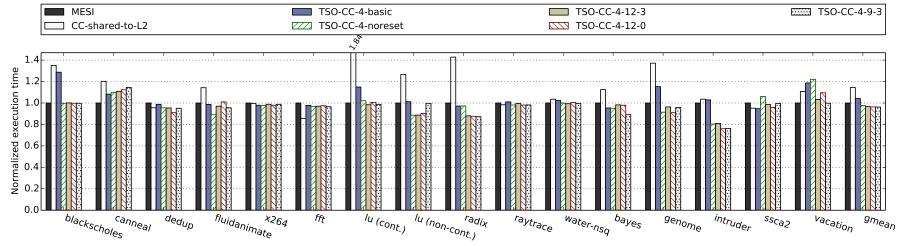

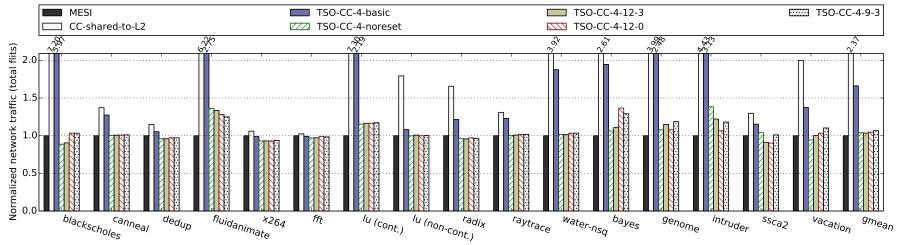

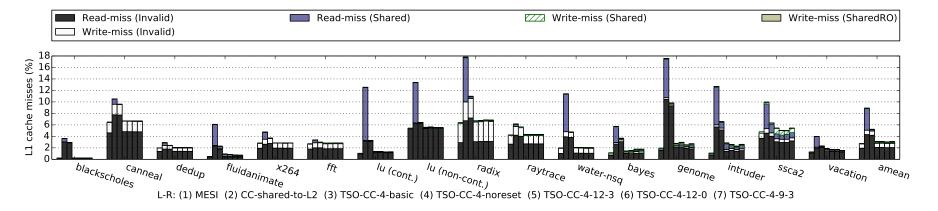

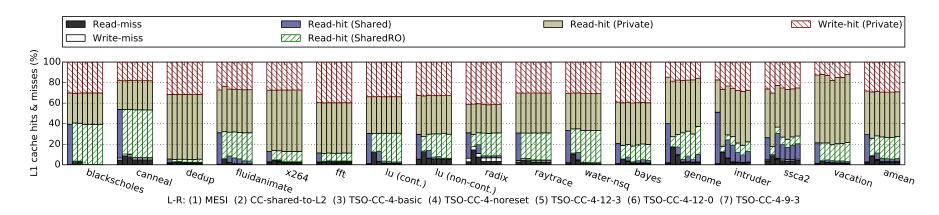

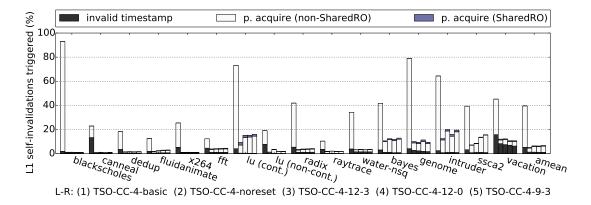

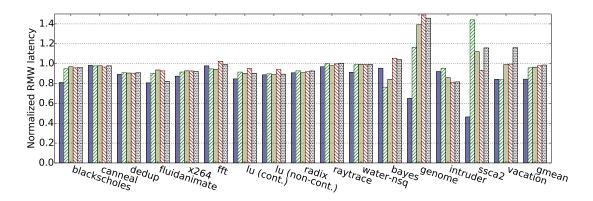

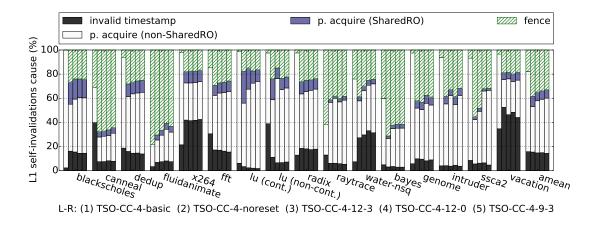

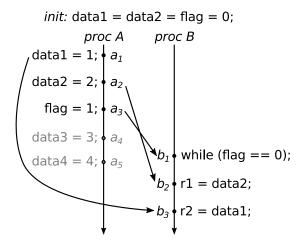

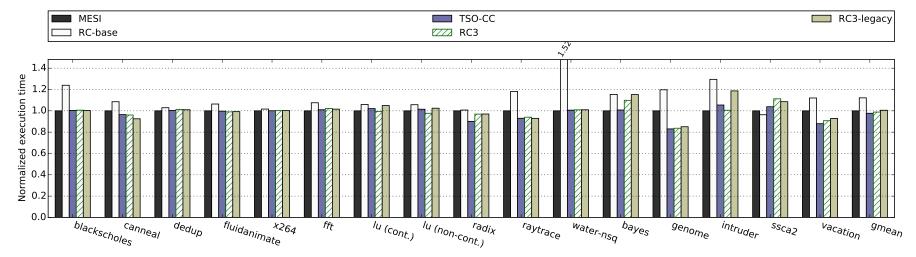

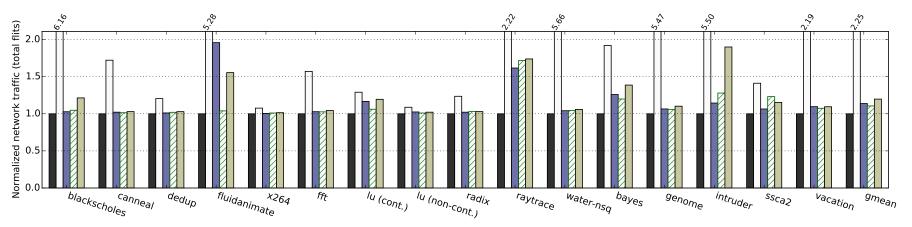

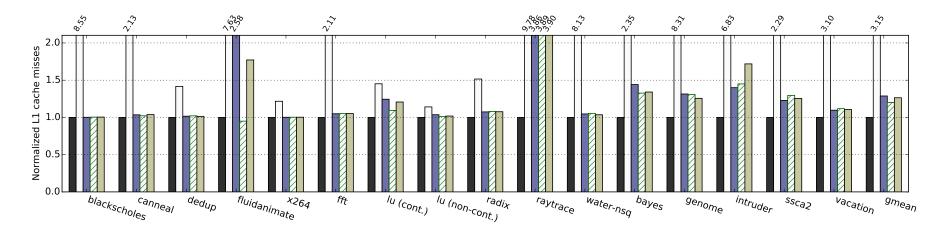

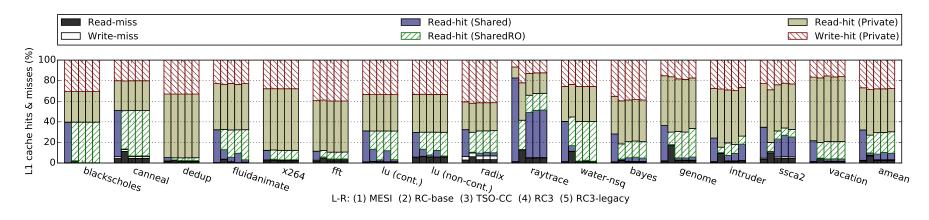

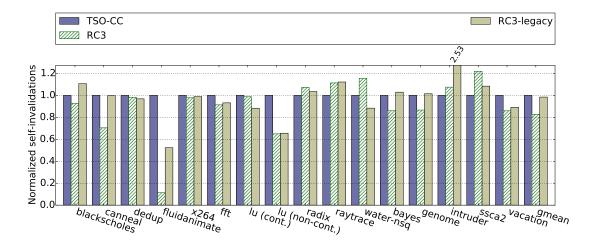

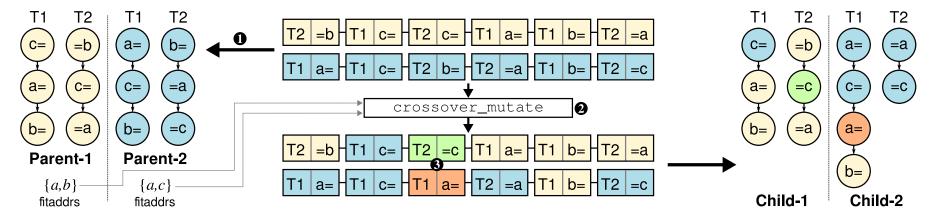

(§3.4) can violate the SWMR invariant, but still satisfy the target consistency model (albeit usually not SC, but rather some form of SC for DRF; see §2.5). Despite such protocols breaking the established norm, it has been argued that this new class of protocols can still be called a cache coherence protocol [Cho+11; SKA13; SA15; SAA15], as their primary objective ("making caches transparent") is unchanged; indeed, they satisfy at least Definition 3.3 [SA15].